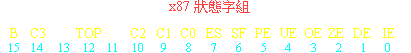

�Ȧs���O�b CPU ���@�ӼȮ��x�s��ƪ��a��C�����I��O���� ( DRAM )�A���O�����O����o��j�A�@�ӼȦs���u���@�ӡB��өΥ|�Ӧ줸�ժ��j�p�A��F AMD64�BINTEL64 ( �ΦX�� x86-64 ) �� CPU �ɥN�A�Ȧs���~���|�r�� ( QWORD�A�@ 64 �줸 ) ���j�p�CCPU �i�H������Ȧs���@�[�B��B���B���B�B�B�ΡB�h�����B��C8086/8088 �@�� 14 �� 16 �줸���Ȧs���A��W�ٳ��H��ӭ^��r���ܡA�j�P�i�����H�U�|���C

�o�|�ӼȦs���]�i�H������� 8 �줸���Ȧs���ӨϥΡA�Ҧp AX �i�Q�������C�� 8 �줸�٬� AL�A�H�θ����� 8 �줸 AH �ӨϥΡC��l BX�BCX�BDX �]�������C

�����η|�n�N��Ʀs�J���|���O�H���n�X�ر��ΡA�Ҧp�I�s�Ƶ{���ɡA�|�w�����^��}�s�J���|�Q�I�s���_�ɤ]�O�p���CBP �q�`�Ω�I�s�Ƶ{���ɡA�ǻ��ѼƤ��ΡC

IP (instruction pointer�A�٬����O����) �t�X CS �ܦ� CS:IP�A���V�N�n���檺 8086/8088 ��}�C�� CPU �n����{���ɡA������O����h�����n���檺���O�A�ӭn�쨺�@�ӰO�����}�h�������O�O�H�o�� CPU �N�|�� CS:IP ���쪺��}�h�����C�b�{�����A�@��O�S����k���� CS:IP ���ȡA���D�O���D (jmp�Bjz��) ���O�άO�I�s (call�Bret��) ���O�C

SI (source index�A�٬��ӷ����Ȧs��) �M DI (destination index�A�٬��ت����Ȧs��) �q�`�O�Ψӷ��@��}���СA�]�i�Χ@�[��k�C�o���ӼȦs���A�C�@�ӳ�������}�ӷ��@��� 8 �줸���Ȧs���ϥΡC

����ưϬq�����ήɡA�N�i�H���B�~�Ϭq�Ӹɨ��A�Ҧp�Q�n�N�@�ӰϬq���Y�Ǥ��e�ƻs��t�@�Ϭq���A�N�i�H�P�ɫ��w DS�BES ���O���ܳo��ӰϬq�C

�o 9 �ӺX�Хi�����T���G���A�X�� ( status flag )�B����X�� ( control flag ) �P�t�κX�� ( system flag )�C���A�X�Х]�t CF�BPF�BAF�BZF�BSF �M OF�A���̷|�����N�B�������B��G���A���v�T�A�ӨϺX�гQ�]�w ( set�A��Ȭ� 1 )�A�γQ�M�� ( clear�A��Ȭ��s )�C�� 10 �줸�� DF �Ψӱ���y�B�h���B�j�M�r�ꪺ��V�A�ݩ�X�СC�ܩ� IF�BTF ���]�p�@�~�t�ΡB�����ɤ~�ݭn�Ψ�A�ݩ�t�κX�СA�@�����ε{���ܤ֨ϥΡC���U²�椶�гo�ǺX�СG

| �W�� | �줸 | ���A | ���� |

| �i��X�� carry flag CF | 0 | CF=1�ACY CF=0�ANC |

���B��o�Ͷi��έɦ�ɡACF �Q�]�� 1�F�Ϥ��]�� 0�C�Ҧp��Ƭۥ[�G

mov ax,8000h

8000h��8000h ���� 10000h�A�o�Ͷi��A���M AX �� 0�A���O�|�� CF �]���@�A���ܶi��Cadd ax,8000h |

| �P��X�� parity flag PF | 2 | PF=1�APE PF=0�APO |

�B�⪺���G�����G�i���A�̧C�� 8 �Ӧ줸���A�Y�����ƭ� 1�A�h���줸�]�� 1�A�Ϥ��� 0�C |

| ���U�i��X�� auxiliary carry flag AF | 4 | AF=1�AAC AF=0�ANA |

���B��L�{���A�� 3 �줸�P�� 4 �줸�����o�Ͷi��έɦ�ɡAAF �Q�]�� 1�A�_�h�Q�]�� 0�A�`�Ω� BCD ���B��C |

| �s�X�� zero flag ZF | 6 | ZF=1�AZR ZF=0�ANZ |

�B��G���s�ɡAZF �|�Q�]�w�� 1�C�Y����ۦP��ơA ZF �]�|�Q�]���@�A�Y������ۦP����ơAZF �|�Q�M�����s�C�Ҧp�G

mov ax,8000h

�ۥ[��AAX ���s�A�G ZF �]���@�Cadd ax,8000h |

| �Ÿ��X�� sign flag SF | 7 | SF=1�ANG SF=0�APL |

�B��G���̰��줸�� 1 �ɡASF �|�Q�]�� 1 ( ���ܭt�� )�A�_�h�Q�M���C |

| �����X�� trap flag TF | 8 | �@ | �Ω��B�l�ܰ����ɡA�ҥH�]�٬��l�ܺX�� ( trace flag )�A�Ҧp�b MS-DOS �� DEBUG ���A�N�O�Q�� TF �F���B�l�ܪ��ت��C�� TF �]���@�ɡA�C����@�ӫ��O�K�|�o�ͤ��_�A�����_�N�N����ӫ��O��Ȧs���C�X�C |

| ���_�X�� interrupt flag IF | 9 | IF=1�AEI IF=0�ADI |

�� IF �Q�]�w�ɡA�i�B�n���w�餤�_�~��� CPU ���ͤ��_�ĪG�F�Ϥ��Ҧ��i�B�n���w�餤�_���|�Q����C���O���i�B�n���_�H�� CPU ���ͪ��ҥ~�o�������� IF �v�T�C |

| ��V�X�� direction flag DF | 10 | DF=1�ADN DF=0�AUP |

�� DF �Q�M���� ( �Y DF=0 )�A�B�z�r�ꪺ���Ȧs���|���W�A������}��V�B�z�A�Ϥ��h����C |

| ����X�� overflow flag OF | 11 | OF=1�AOV OF=0�ANV |

���B��G�L�k�e�ǩ�ت��B�⤸���A���X�з|�Q�]���@�C�j�P�i���T�ر��ΡG(1)��P���Ƭۥ[�Ψⲧ���Ƭ۴�A(2)�����B��ɡA�ұo���n�ΰӶW�L�B�⤸�s��d��A�b����α�����O�ɡA�̰��줸�Ȩ����� ( 0 �ܦ� 1 �� 1 �ܦ� 0 )�C( �Բӱ��νаѾ\�� 35 �������C ) |

�W�����������X�мȦs�����N�q�C�H�X�мȦs�����줸 0 ���ҡA�줸 0 �٬��y�i��X�Сz�A�����Q�]�w�ɡA��Ȭ� 1�A�b DEBUG �إH CY ���ܡF�Q�M���ɡA��Ȭ� 0�A�b DEBUG �إH NC ���ܡC���U�C�X DEBUG ������ r ���O�᪺�N�q�G

-r [Enter] AX=0000 BX=0000 CX=0025 DX=0000 SP=FFFE BP=0000 SI=0000 DI=0000 DS=10F7 ES=10F7 SS=10F7 CS=10F7 IP=0100 NV UP EI PL NZ NA PO NC 10F7:0100 EB19 JMP 0119

�զ⪺�����N�O�X�Ъ����A�A�ЬݤU���G

| �X�ЦW�� | �]�w(1) | �M��(0) |

|---|---|---|

CF�A�i��(�O/�_)

PF�A�P�� ( ����/�_�� )

AF�A���U�i�� ( �O/�_ )

ZF�A�s ( �O/�_ )

SF�A�Ÿ� ( �O/�_ )

IF�A���_ ( ���\/���� )

DF�A��V ( ����/���W )

OF�A���� ( �O/�_ ) |

CY

PE

AC

ZR

NG

EI

DN

OV |

NC

PO

NA

NZ

PL

DI

UP

NV |

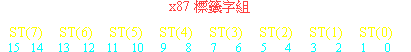

�̦��ϥΦb IBM PC �άۮe���ت� FPU �O 8087�A��ӤS���O���i���� 80287�B80387�A�o�̦X�٬� x87�Cx87 �@�������Ȧs���A���̬O���|�Ȧs�� ( register stack )�B���A�r�� ( status word )�B����r�� ( control word )�B���Ҧr�� ( tag word )�B�ҥ~���� ( exception pointer )�C

x87 �@���K�Ӱ��|�Ȧs���A��W�٬O ST(0)�BST(1)�BST(2)�K�KST(7)�A�䤤 ST(0) �Q�٬����|�� ( TOS�ATop Of Stack )�A�b�զX�y�����]�i²�g�� ST�C�o�K�Ӱ��|�Ȧs���C�@�ӳ��� 80 �줸���j�p�Ӧs��B�I�ơA�åB�H�Ȯɹ�ƪ��κA�s��A�i�H���۷����ǽT�C�� x87 ���� FLD�BFILD �����O�A�q�O���餤����ơB�u��Ƶ����P�榡���J�ƭȮɡAx87 ��۰��ഫ���Ȯɹ�Ʈ榡����|�Ȧs���ءF�� x87 �J�칳 FIST�BFST �����O�A�n����|�Ȧs�������ƭȦs�J�O���餤�Ax87 �|�۰��ഫ���ҫ��w���榡�C

x87 �i�H����\�h�������p��A�p�D�����B�l���B��ơK�K���B��A���O�H���|�Ȧs�������Ȯɹ�Ƭ��B�⪺��ơA�]���]�٬���ƼȦs�� ( data register )�C���\�h���B�ⳣ�O�|�o�A�� TOS �A���ɤ]�� TOS �M��L���|�Ȧs�����B��A�ҥH TOS �`�`�O�i�H�ٲ��A�{���]�p�v�o�p�߳o�ءy���t�z���g�k�A�H�K�y���x�Z�C

�o 8 �Ӱ��|�Ȧs�����W�١AST(0)�BST(1)�BST(2)�K�K�����A�ä��O�T�w���Y�Ӱ��|�Ȧs���C�ӬO�Ѫ��A�r�� ( ���U���� ) ���T�� ST �줸���w���|���A�ӤU�@�Ӱ��|�Ȧs���N�O ST(1)�B�A�U�@�ӴN�O ST(2)�K�K�C

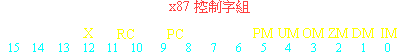

�o�� 16 �줸���Ȧs���M�w�F x87 �藍�P�ҥ~���B�z�B�p��ˤJ�B�����ƺ�T�����C����r�ժ��U�����p�U�ϩҥܡG

| RC | �ˤJ���� | ���� | �Ҥl |

| 00 | �|�ˤ��J | �V�̪�� �{�|�˥h�A�J���i�� |

4.5 ==> 5 -4.5 ==> -5 |

| 01 | �V�t�L�a�j�ˤJ | ���ȱ˥h�p�Ƴ��� �t�ȱ˥h�p�Ƴ�����A��@ |

4.5 ==> 4 -4.4 ==> -5 |

| 10 | �V���L�a�j�ˤJ | ���ȱ˥h�p�Ƴ�����A�[�@ �t�ȱ˥h�p�Ƴ��� |

4.5 ==> 5 -4.5 ==> -4 |

| 11 | �V�s�˥h | ���ץ��t�ȧ��˥h�p�Ƴ��� | 4.5 ==> 4 -4.5 ==> -4 |

00 ���� 24 �줸���ļ� 01 �O�d���ϥ� 10 ���� 53 �줸���ļ� 11 ���� 64 �줸���ļơ@�@���w��

IM�BDM�BZM �o�T�Ӧ줸�O x87 �b������O���e�A�N����쪺�FOM�BUM�BPM �h�O�b���O�����A�~�����C

�U�W��q�A�o�ӼȦs���O�ΨӪ��� 80x87 ���A���A�䵲�c�p�U�ϡG

8087 ���@�� 16 �줸�����Ҧr�աA���Ҧr���ئ��K�Ӽ��ҡA�C��Ӧ줸���@�Ӽ��ҡA���O������K�Ӱ��|�Ȧs���C�p�U�ϡG

�C�Ӽ��ҥN���۹��������|�Ȧs�����s�J���ƭȧκA�C

8087 �ү�B�z���ƭȸ�ƧκA�A���F�C�ذκA ( �r�վ�ơB�u��ơB����ơB�u��ơB����ơB�Ȯɹ�ơB�E�� BCD ��� ) ���~�A�٫O�d�F�Y�ǯS�����s�X�覡�Ӫ��ܯS������ơA�o�ǯS������Ƥ@�����ΤW���֨ϥΡA�i�ѦҲ� 22 �����|�������C

�ҥ~���Х]�t�T�ӼȦs���G���O���мȦs�� ( last instruction pointer )�B�B�⤸���мȦs�� ( last operand pointer�A�]�s��ƫ��мȦs���Alast data pointer )�B���O�X�Ȧs�� ( last instruction opcode )�C�o�T�ӼȦs���Ω�ҥ~�o�ͮɡA���{�����D�o�ͨҥ~�ɡAx87 �����污�ΡC���O���мȦs���P�B�⤸���мȦs�����O 48 �줸���A���O�X�Ȧs���� 11 �줸���C

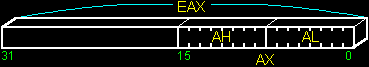

��F���L 74 �~�Q��A�^�S�����X�F�s�@�N�� CPU�A80386�C�N�զX�y�����[�I�ӬݡA�o�� CPU �P���e�� 8086/80286 ���ܤj�����P�A���㦳 32 �줸�Ȧs���A�i�H�@���� 32 �줸�B��A�@���� Pentium 4 ����A�q�μȦs���B���лP���Ȧs���B�Ϭq�Ȧs���B�X�мȦs�����ۦP�C

80386 ���q�μȦs���@�� 4 �ӡA���O�O EAX�BEBX�BECX�BEDX�A���̪��W�٩M 8086/80286 �q�μȦs���W�٫ܬۦ��A�e�����yE�z���ܡyextended�z�A�������N�C�o�|�� 32 �줸���q�μȦs���A�C�@�Ӹ��C�r�ժ� 16 �줸�S�i�W�ߦ��@�� 16 �줸���Ȧs���A�W�ٻP 8086 �ۦP�C�ӳo�C�r�ժ� 16 �줸�Ȧs���S�i�A�������줸�ժ� 8 �줸�P�C�줸�ժ� 8 �줸��ӼȦs���C�Ҧp EAX ���C�r�ժ� 16 �줸�� AX �Ȧs���AAX �S�i���� AH �P AL ��ӤK�줸���Ȧs���A���O EAX �����r�ժ� 16 �줸�L�k��W�ϥΤF�A�]�S�S�����W�١C�ܩ� EBX�BECX�BEDX �]�M EAX �ۦP�A���U�ϡC

80386 �� 4 �� 32 �줸�����лP���Ȧs���A���O�O ESP�BEBP�BEIP�BESI�BEDI�A�ӨC�@�ӤS�i�H����C�� 16 �줸��X�ӨϥΡA���O�٬� SP�BBP�BIP�BSI�BDI�A�P�˪��������r�յL�k��W�ϥΡA�]�S�S�����W�١C�o�ǼȦs�����Ϊk�P 8086/80286 �ۦP�A�Ҧp�b�ϥ�

rep movsb

�ɡA�N������ӷ��r���}�s�� ESI�A�ت��r���}�s�� EDI�A���ʪ��줸�ռƦs�� ECX�C

80386/80486/Pentium ������ 16 �줸���Ϭq�Ȧs���A���O�O CS�BDS�BES�BSS�BFS �M GS�A�� 8086/80286 �h�X��ӡAFS �M GS�C�e���|�Ӫ��Ϊk�P 8086/80286 �ۦP�A�Ҧp CS ���V�{���X�Ϭq�BDS ���V��ưϬq�C�h�X�Ӫ� FS �M GS �i�����B�~�Ϭq�C���O�b�O�@�Ҧ����Ϭq���N�q�P�u��Ҧ����P�A�аѦҫO�@�Ҧ������m�C

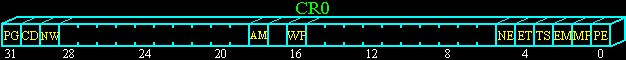

�P 8086 �� 16 �줸�X�мȦs������A80386/80486/Pentium �������X�мȦs���� 32 �줸�e�A���M�h�F�@�Ǥj�����P�O�@�Ҧ������t�κX�СA�����M���\�h�줸���Q�ϥΡA�åB����X�лP���A�X�г���P 8086 �ۮe�C�U�ϬO�����X�Ъ��U�줸�W�١G

| �W�� | �줸 | ���� |

| I/O �S�v���� I/O privilege level | 12�B13 | ����줸�O�ΨӨM�w�{���O�_���\�s�� I/O ��ΰ���ݭn�S�v���ū��O ( �p lgdt�Bmov cr0,ax ���� )�A���{�����S�v���� ( CPL ) �p��ε��� IOPL �ɡA�~�i�H�s�� I/O ��ΰ���ݭn�S�v���ū��O�C�`�N�A�b 386 �Ψ䰪�� CPU ���O�@�Ҧ����A�@���� RING0�BRING1�BRING2�BRING3 �|�دS�v���šARING0 �O�̰��šA�@��@�~�t�ΡB�X�ʵ{�����b�o�ص��ŤU����CRING3 �O�̧C���šA�@�����ε{���b RING3 ������C |

| Task �걵�X�� nested task NT | 14 | ���X�ХΨӪ��ܥثe���檺�{�� ( task ) ���e�O�_�٦���L�{�����ݳQ����A�Y NT=1�A�����٦��{�����ݰ���F�Ϥ��h�_�C |

| �^�_�X�� resume flag RF | 16 | ���X�ХΨӬO�_�Ȯɧ�����ҥ~�A�Y RF=1�ACPU �|�h�B�z�����ҥ~�A�Ϥ����|�C |

| ���� 86 �Ҧ� virtual 86 mode VM | 17 | ���� 86 �Ҧ� ( V86 mode ) �i�����@�دS�����O�@�Ҧ��ACPU �n���i�J�O�@�Ҧ�����A�~�i�i�J V86 �Ҧ��A�ҥH�� VM=1 �ɬ� V86 �Ҧ��FVM=0 �ɬ��O�@�Ҧ��C |

| ����ˬd alignment check AC | 18 | �� AC �P CR0 �Ȧs���P�ɬ��@�ɡACPU �|�ˬd�O����s����}�O�_����A�S��������s���ʧ@�|���͡y����ˬd�ҥ~�z�C�ҿסy�ˬd�O����s����}�O�_����z���N��O�G���s���r�� ( word ) ��ƫ��A����ƩҦb��}�����O 2 �����ơB�s�����r�� ( dword ) ��ƫ��A����ƩҦb��}�����O 4 �����ơC |

| �������_�X�� virtual interrupt flag VIF | 19 | �Ω�h�u���ҤU�䴩���_�X�СC |

| �������_�a�m�X�� virtual interrupt pending flag VIP | 20 | �Ω�h�u���ҤU�䴩���_�X�СC |

| �ѧO�X�� identification flag ID | 21 | �p�G���ε{���i�H�M���γ]�w�ѧO�X�СA���� CPU �䴩 CPUID ���O�C |

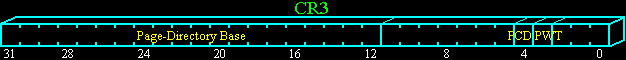

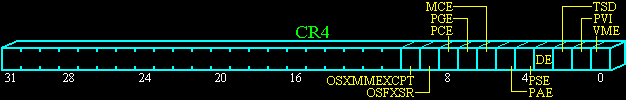

80386/80486/Pentium �ϥΥ|�ӰO����z�Ȧs���ӰO���O�@�Ҧ����U�A�O����y�z�������}�Ҧb�A���̬O�G

80386/80486 ���|�ӱ���Ȧs���A���O�O CR0�BCR1�BCR2�BCR3�APentium �٦h�F�@�� CR4�C